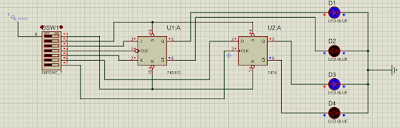

2. Alat dan Bahan (kembali)

b. D flip-flop 74LS74

c. Switch DIPSWC_7

d. 4 LED biru

e. Power dan Ground

1.) Jelaskan prinsip kerja rangkaian percobaan 4!

Rangkaian ini gabungan dari J-K flip-flop dan D flip-flop. Rangkaian ini bersifat aktif low pada kedua pin Set dan Reset nya. Sementara itu, pin Clock pada komponen J-K flip-flop juga bersifat aktif low, dan clock pada komponen D flip-flop bersifat aktif high.

Pada J-K flip-flop dengan pin Set dan Reset aktif low, maka ketika input pada pin Set berlogika 1 dan Reset berlogika 0, maka nilai output pada pin Q akan berlogika 0 dan pada pin Reset berlogika 1. Kondisi ini disebut dengan mode operasi Reset. Berlaku sebaliknya, saat pin Set berlogika 0 dan pin Reset berlogika 1, maka output Q berlogika 1 dan Q Not 0. Kondisi ini disebut dengan mode operasi Set. Sedangkan, apabila kedua input Set dan Reset berlogika "0", maka disebut juga dengan mode terlarang dimana kedua outputnya berlogika "1". Ketiga kondisi tersebut akan mengabaikan input J, K, dan clock.

Ketika input Set dan Reset berlogika 1, dan input J dan K dirubah menjadi 0 dan 1, input clock akan diabaikan. berlaku juga jika input J dan K dirubah menjadi 1 dan 0, input clock juga akan diabaikan. Jika Kedua input J dan K berlogika 1 , output pada Q dan Q not akan berubah-ubah, ini disebut kondisi toggle yang dipengaruhi perubahan pada clock yaitu dalam keadaan fall time.

Pada D flip-flop, ketika pin Set berogika "0" dan pin Reset berlogika "1", output Q akan berlogika 1 dan Q Not berlogika 0. Kondisi ini disebut dengan mode operasi Set. Sebaliknya, saat pin Set berlogika 1 dan pin Reset berlogika 0, maka output Q berlogika 0 dan Q Not berlogika 1. Kondisi ini disebut dengan mode operasi Reset. Sedangkan, apabila kedua input Set dan Reset berlogika "0", maka disebut juga dengan mode terlarang dimana kedua outputnya berlogika "1". Ketiga kondisi tersebut akan mengabaikan input D dan clock.

Apabila kedua input Set dan Reset berogika "1", ketika input D diubah menjadi berlogika "1", maka output Q dan Q Not-nya akan berlogika "1" dan "0". Ketika input D berlogika "0", maka akan menjadi sebaliknya. Kedua kondisi ini akan mengabaikan input clock saat clock dalam keadaan Rise. Apabila input clock dalam keadaan Fall, input D akan diabaikan dan output Q dan Q Not-nya akan tetap seperti keadaan sebelumnya.

2.) Jika saklar B0 berlogika "0", maka bagaimana kondisi output?

Terdapat dua kondisi yaitu saat B0 = 0 dan B1 = 0 atau B0 = 0 dan B1 = 1 . Saat kondisi B0 = 0 dan B1 = 0, maka output pada J-K flip-flop maupun D flip-flop dalam kondisi terlarang. Sementara itu, saat kondisi B0 = 0 dan B1 = 1, maka output Q dan Q Not pada J-K flip-flop maupun D flip-flop akan berlogika 0 dan 1.

Vidio [ Download ]

Tidak ada komentar:

Posting Komentar